La expresión «lógica programada» (o «lógica programable») hace referencia a la posibilidad de establecer la operativa lógica de un circuito integrado definiéndola por medio de un lenguaje que permite describirla a un nivel más o menos alto y que puede posteriormente ser traducida para implementarla en el dispositivo lógico, bien durante su fabricación o bien posteriormente.

La lógica programada (o programable), en contraposición a la «lógica cableada», permite fabricar circuitos integrados más o menos genéricos, sin unas funciones lógicas predeterminadas, y definir y almacenar posteriormente su funcionamiento e incluso modificarlo después. La expresión lógica cableada haría así referencia a la que se implementa definiéndola a nivel físico.

La lógica programada requiere de software, la descripción de su funcionamiento, y de hardware, los circuitos integrados que soportan dicho funcionamiento. El software de la lógica programada suele expresarse a alto nivel conforme a un lenguaje de descripción de hardware, HDL por sus siglas en inglés Hardware Description Language. El proceso de obtención de la información que permite implementar la lógica en los circuitos integrados se suele denominar síntesis.

Como se ha dicho, el hardware usado en la lógica programada puede ser de tipo genérico, en tal caso, a los circuitos integrados se los conoce como dispositivos lógicos programables o PLD, por las siglas en inglés de Programmable Logic Device. que se fabrican sin almacenar ninguna lógica y que es necesario definirla (programarla) antes de utilizarlos.

Cuando el hardware es de tipo específico se denominan, ASIC, por la expresión, en inglés, Application Specific Integrated Circuit o circuitos integrados de aplicación específica. Aunque en algunos casos su funcionamiento puede ser más o menos redefinido, básicamente los ASIC se entregan definidos de fabrica y sus prestaciones, especialmente en lo referido a velocidad, suelen ser mucho más altas que la de los PLD. Actualmente su integración es muy alta y es frecuente que incluyan o estén formados también por procesadores y distintos tipos de memorias. En tales casos es habitual referirse a ellos como SoC, del inglés System on a Chip, es decir, sistema en un chip. También es posible integrar en un único componente procesadores, memoria y lógica programable (fuera de fábrica, por el usuario) en estos casos, el dispositivo toma el nombre de «system on a programmable chip» (SoPC), sistema en un chip programable.

En sentido estricto, los ASIC podrían entenderse como pertenecientes a la lógica cableada ya que salen de fábrica con la lógica implementada en el hardware pero suelen agruparse más frecuentemente con los dispositivos de la lógica programada puesto que se valen de las técnicas de programación de lógica basadas en los lenguajes HDL. Además, en muchos casos, los ASIC no son dispositivos completamente definidos para cumplir cierta función específica (caso al que se hace referencia con la expresión full-custom o totalmente configurados) sino que son parcialmente modificables (semi-custom o parcialmente configurados) lo que amplía la posibilidad de usarlos en aplicaciones diversas y justifica más su clasificación como parte de la lógica programada.

Los PLD representan el estado actual de la evolución de los dispositivos lógicos discretos. Por una parte, los modernos métodos de fabricación permiten un grado de integración muy alto comparado con el que era posible en los primeros dispositivos TTL. Por otro lado, al tratarse de dispositivos inespecíficos, de aplicación muy flexible, pueden fabricarse masivamente lo que, por la economía de escala a la que acceden, los abarata considerablemente haciéndolos asequibles además de potentes y versátiles.

La lógica de los microcontroladores, la de los procesadores de señal (DSP) o la de los microprocesadores, se determina por la ejecución en los mismos de unas instrucciones software almacenadas en una memoria (programa) que deben ir leyendo. La lógica programada, por contra, se establece a nivel de hardware, es decir, una vez definida la forma en la que van a trabajar, se aplica al dispositivo lógico dándole «forma física» a su comportamiento de manera que no necesitará leer previamente unas instrucciones e ir ejecutándolas sino que habrá quedado establecido su funcionamiento. Debido a esta característica diferenciadora, también se la denomina lógica programada por hardware, que es un término más preciso aunque menos usado. Por contraposición, la lógica usada en los microcontroladores, en los procesadores de señal o en los microprocesadores sería la lógica programada por software.

Según lo que se ha explicado, podrían hacerse diferentes clasificaciones de los dispositivos lógicos en función del criterio al que se atienda principalmente.

-

Si se trata de dispositivos en blanco, cuya lógica se implementa después de fabricados, se haría referencia a su funcionamiento lógico como lógica programada frente a la lógica cableada de los dispositivos que ya disponen de ella al salir de fábrica. Como se ha dicho, aunque es discutible, los ASIC se suelen incluir en la lógica programada.

-

Cuando la lógica se obtiene de una lista de instrucciones (programa) almacenada en memoria se trataría de lógica programable por software frente a la lógica implementada en la circuitería que se denomina lógica programada por hardware. Típicamente, los microcontroladores y los microprocesadores forman parte del primer grupo y los dispositivos lógicos programables del segundo.

-

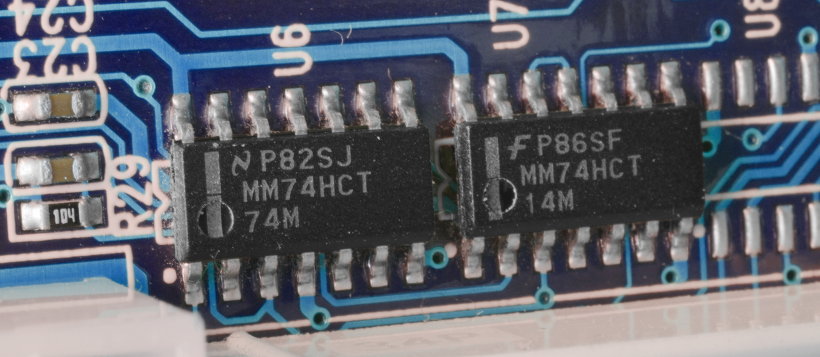

Los primeros circuitos integrados lógicos (puertas lógicas, multiplexores, demultiplexores, codificadores, decodificadores…) por ejemplo los pertenecientes a la serie 74LS, formaban una serie de dispositivos lógicos de funcionamiento específico para aplicación genérica que se denomina lógica de catálogo en contraposición a la lógica de propósito general (o genérica) que permite utilizar un dispositivo y programarlo expresamente para una aplicación específica. La lógica de catálogo también se conoce como lógica convencional.

-

Mientras que los PLD pertenecen a la clasificación de circuitos integrados IC de uso general (referidos frecuentemente en inglés como general purpose use) los ASIC corresponden a categoría de circuitos integrados IC de aplicación específica. Un punto intermedio entre ambos podrían ser los ASSP, siglas en inglés de o productos estándar de aplicación específica.

Por su enfoque, quedan fuera de este texto otras clasificaciones relativas a la lógica programada como por ejemplo las relacionadas con las tecnologías de fabricación o las relativas a su composición y funcionamiento interno.

El hardware de la lógica programable

Los circuitos integrados utilizados en la lógica programada cuya funcionalidad se habilita después de finalizado el proceso de fabricación, es decir, los de tipo genérico, se denominan habitualmente dispositivos lógicos programables o PLD pero, como se verá seguidamente, esa denominación engloba en realidad a varios tipos de dispositivos.

Memorias usadas como PLD

Las precursoras de los PLD fueron las memorias ROM (de sólo lectura: Read Only Memory en inglés) utilizando como entradas las líneas de dirección y las de datos como salidas de manera que en ellas se podía representar el resultado lógico que estuviera almacenado en la memoria ROM. Actualmente no se utilizan profesionalmente ya que sólo se aprovecha de ellas, según este uso, una fracción de su capacidad, son más lentas y de mayor consumo que los integrados específicos y sobre todo por no ser una solución adecuada a la lógica secuencial ya que para ella necesitan de biestables en circuitos externos.

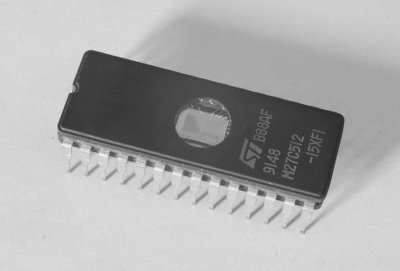

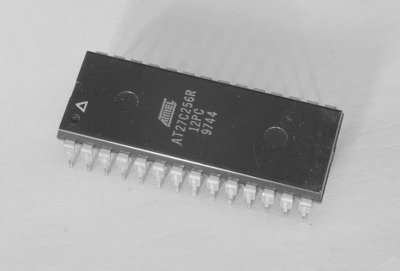

Antes de la aparición en el mercado de los primeros dispositivos lógicos programables en sentido estricto, se utilizaron para la lógica programada algunas mejoras sobre las memorias ROM, como las ROM asociativas o ROAM por las siglas Read Only Associative Memory en inglés, o las programables PROM, por Programmable Read Only Memory.

Después de los avances de las memorias ROAM se desarrollaron los primeros PLD tal como se entienden ahora; fueron las matrices lógicas programables, PLA, por su nombre en inglés Programmable Logic Array. Al tratarse de una tecnología temprana coexistieron diferentes alternativas antes de llegar a su posterior madurez. Algunas PLA eran programables como parte del proceso de fabricación y otras borrables utilizando luz ultravioleta. En general se trataba de dispositivos bastante limitados; sin biestables (lo que impide su uso en lógica secuencial sin añadir circuitos externos) o con pocos biestables y con pocas entradas y salidas.

PAL: Programmable Array Logic (matrices lógicas programables)

Las matrices lógicas programables, PAL (del inglés Programmable Array Logic) fueron los primeros PLD con una presencia muy relevante en el mercado. Su éxito radicó en la sencillez comparativa que las hacía más compactas, rápidas y baratas.

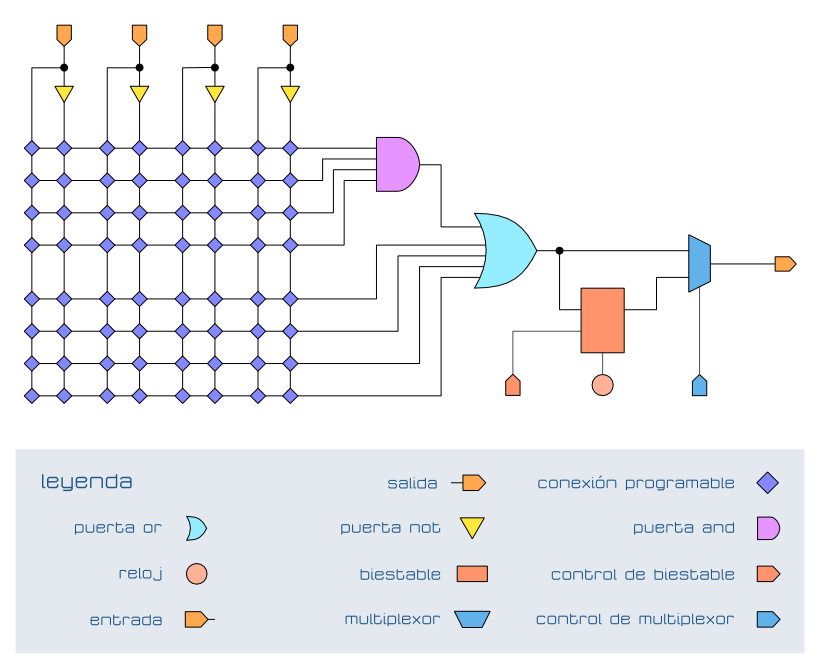

Las PAL estaban formadas por una matriz de unos pocos cientos de puertas lógicas AND que pueden ser activadas (programadas) y que están conectadas a una serie de puertas OR fijas lo cual permite implementar una suma de productos. A la salida de las puertas lógicas, las PAL contaban también con biestables por lo que podían usarse para lógica secuencial.

Como las memorias PAL sólo podían programarse una vez, su evolución llevó al desarrollo de la lógica programable borrable eléctricamente: PEEL (del inglés, Programmable Electrically Erasable Logic) y al de las mucho más difundidas matrices de lógica genérica GAL (del inglés Generic Array Logic) que mantienen un diseño lógico similar a las PAL pero que además pueden borrarse para volver a programarse posteriormente permitiendo desde corregir errores de diseño hasta realizar mejoras o modificaciones sustanciales sobre el funcionamiento inicialmente previsto.

CPLD: Complex Programmable Logic Device

Todas las tecnologías de PLD de las que se ha hablado hasta ahora, se agrupan en la actualidad en el grupo de los denominados SPLD, por las siglas en inglés de Simple Programmable Logic Device o dispositivos lógicos programables sencillos (sencillos en el sentido de disponer sólo de unos pocos cientos de puertas lógicas) Por su mayor integración frente a los SPLD, actualmente se utilizan los CPLD, que son su evolución en cuanto a prestaciones aunque mantienen, a grandes rasgos, el mismo criterio de diseño. Su nombre corresponde con las siglas en inglés de Complex Programmable Logic Device o dispositivos lógicos programables complejos.

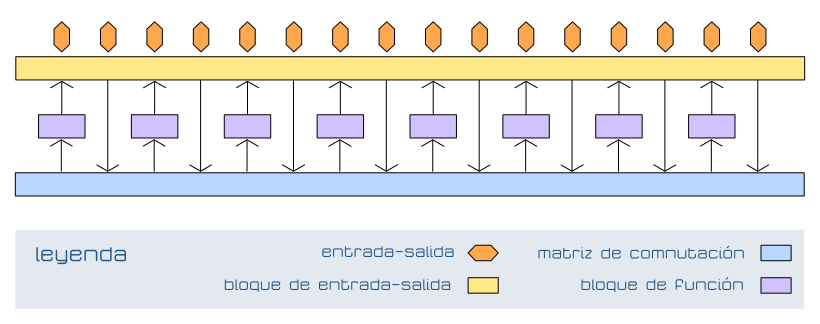

Una de las principales diferencias que permite llamar «complejos» a los CPLD es la agrupación de las matrices de sumas de productos en macroceldas interconcectadas y agrupadas en bloques lógicos o bloques de función (FB, del inglés Function Block) y la gestión de las entradas y de las salidas en bloques de entrada/salida.

Cada una de estas macroceldas sería, esquemáticamente como un PLD completo al que se añade, como entrada, la salida de las otras que forman el CPLD a través de una matriz de conmutación de entradas y salidas. En dicha matriz de conmutación se integra también la salida para conectarla con las otras macroceldas del bloque de función.

FPGA: Field Programmable Gate Array

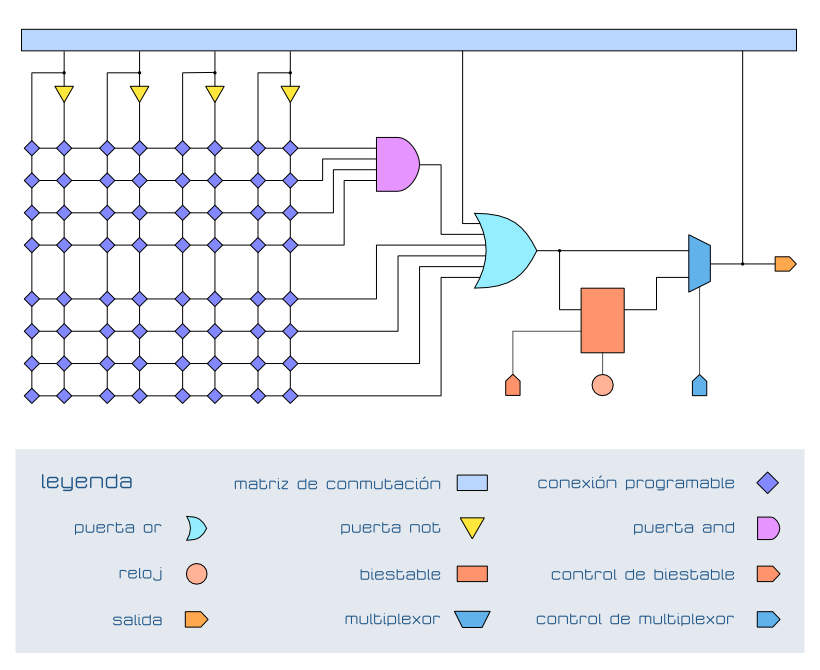

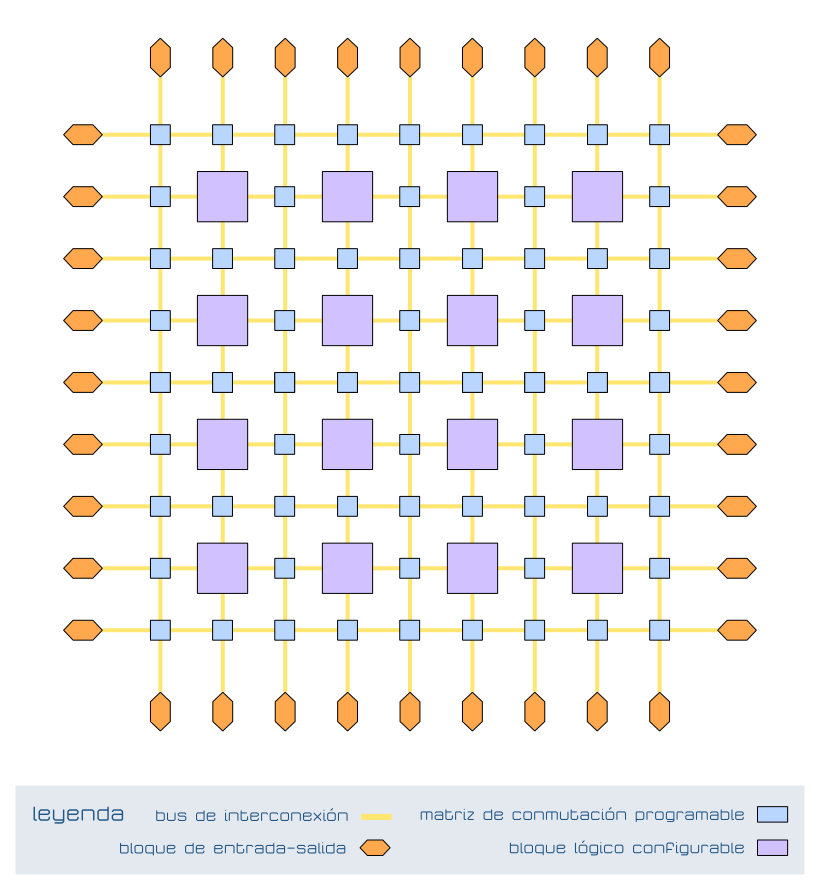

El representante más moderno de los PLD son las FPGA, siglas en inglés de Field Programmable Gate Array o matrices de puertas de campos programables. Mientras que la circuitería de las CPLD esta formada por una serie de sumas de productos cuyas conexiones pueden programarse y conectar con biestables, la arquitectura de las FPGA está formada por bloques lógicos configurables (también con biestables) lo que la hace más flexible. Así mismo, frente a las CPLD las FPGA aportan mayor integración de puertas lógicas (entre 10 y 100 veces más).

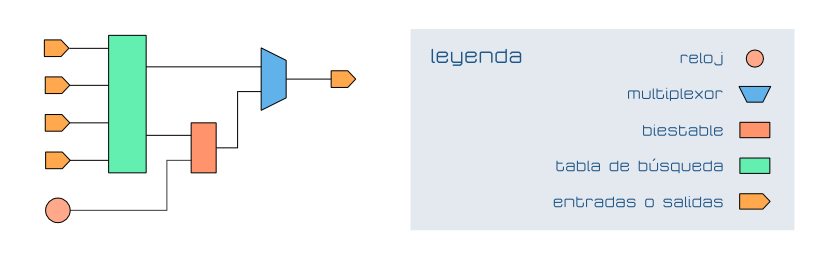

En lugar de calcular los resultados de la lógica combinacional alojada en el PLD por las sumas de productos que correspondan a la función lógica programada, como es el caso de los CPLD, los bloques lógicos de las FPGA utilizan tablas de búsqueda o LUT, acrónimo en inglés de LookUp Table. Las LUT permiten almacenar valores arbitrarios que corresponderán al resultado o salida de una función lógica de determinados valores de entrada. El principio de funcionamiento es similar al de las memorias cuando son usadas como dispositivos lógicos programables: se asimilan las entradas al bus de direcciones y las salidas al bus de datos, almacenando la lógica en la memoria.

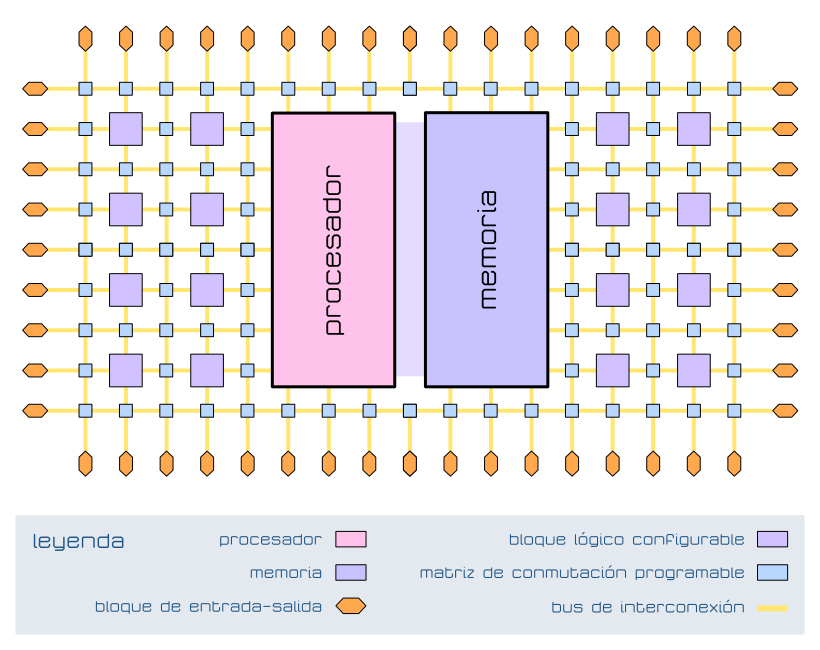

Como puede verse en el gráfico anterior, de una manera esquemática se puede considerar que las FPGA están formadas por una serie bloques lógicos configurables o CLB (siglas de Configurable Logic Block en inglés) que acceden a los bloques de entrada / salida o IOB (siglas de Input/Output Block en inglés) por medio de matrices de conmutación programable o PSM (siglas de Programable Switch Matrix en inglés) que los interconectan.

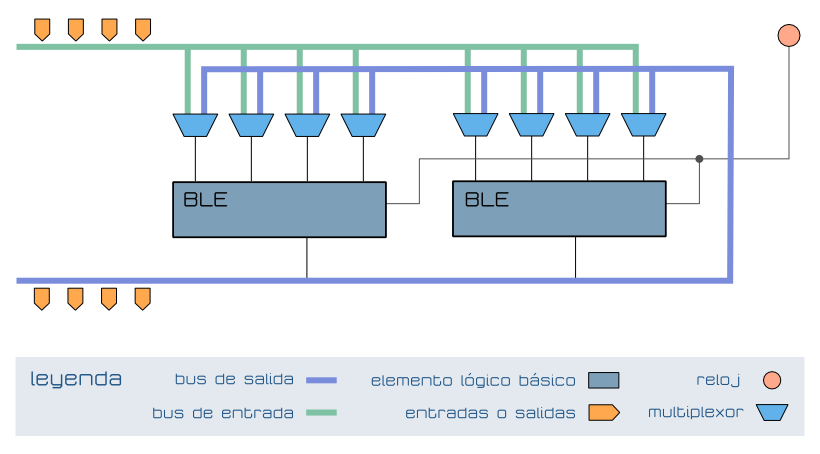

Los bloques lógicos configurables están formados por cierto número de LUT cuyas salidas, multiplexadas, están conectadas a su vez a biestables y a las salidas del bloque. Puesto que todos los niveles requieren de interconexión por medio de multiplexores con los que seleccionar la salida de las LUT, los biestables o directamente las entradas al bloque lógico, el nivel de complejidad crece rápidamente al aumentar la capacidad de las LUT. Como alternativa se pueden utilizar composiciones sencillas, denominados elementos lógicos básicos o BLE (por las siglas de Basic Logic Element en inglés) y agruparlas en clústers lógicos o LC (siglas en inglés de Logic Cluster) que realizan la tarea de los bloques lógicos configurables de una manera más eficientemente escalable.

Por lo que respecta al reducido alcance de este texto, los circuitos integrados de aplicación específica o ASIC, pueden equipararse a las FPGA con la salvedad de que los primeros se programan,aunque no necesariamente por completo, en fábrica y son más eficientes (más rápidos y de menor consumo energético) que las segundas a costa de resultar más caros.

En la actualidad sólo se encuentran comercialmente disponibles CPLD, FPGA y ASIC. En los proyectos que requieran una lógica relativamente sencilla se utilizan CPLD dejando las FPGA a los más complejos. Sólo cuando la funcionalidad está suficientemente bien definida (concretada), la cantidad de circuitos integrados fabricada para el proyecto es suficientemente grande como para que sea económicamente viable o la velocidad es un factor crítico, es preferible utilizar ASIC en lugar de FPGA puesto que, supuesta la misma operativa, como ya se ha dicho, los primeros ofrecen un rendimiento superior a las segundas con un menor consumo energético.

La evolución desde los circuitos integrados usados ya en los sesenta (como la serie 74LS) hasta los dispositivos programables actuales puede resumirse en la siguiente tabla con algunos de los hitos más relevantes de los que se ha hablado.

| 1969 | Motorola | MPGA | 12 puertas y 30 pines de entrada o de salida disponibles en el integrado |

| 1970 | Texas Instruments | PLA | 17 entradas, 18 salidas y 8 biestables Programable durante la fabricación |

| 1971 | General Electric | PLD | Primer PLD reprogramable |

| 1973 | National Semiconductor | PLA | Sin biestables. 14 entradas y 8 salidas Precursor de las FPGA |

| 1974 | General Electric | PALA | Más de 100 puertas disponibles |

| 1978 | Monolithic Memories Incorporated | PAL | Disponían de 8 entradas y 16 salidas |

| 1980 | Ferranti | ULA | Primer circuito integrado ASIC |

| 1983 | Lattice Semiconductor | GAL | Equiparable a una PAL reprogramable |

| 1984 | Xilinx | FPGA | Cientos de miles de puertas lógicas |

Empresas fabricantes y presencia en el mercado

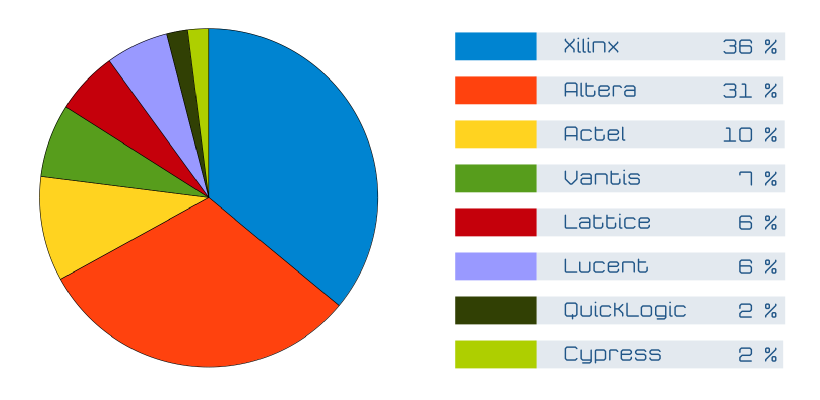

Aunque dependiendo de los productos fabricados, la tecnología usada, la evolución de crecimiento… los datos de volumen de mercado internacional de PLD del segundo trimestre del pasado año (2013) pueden servir como una referencia válida, aunque aproximada, de la presencia en el mercado de los diferentes fabricantes de dispositivos lógicos programables.

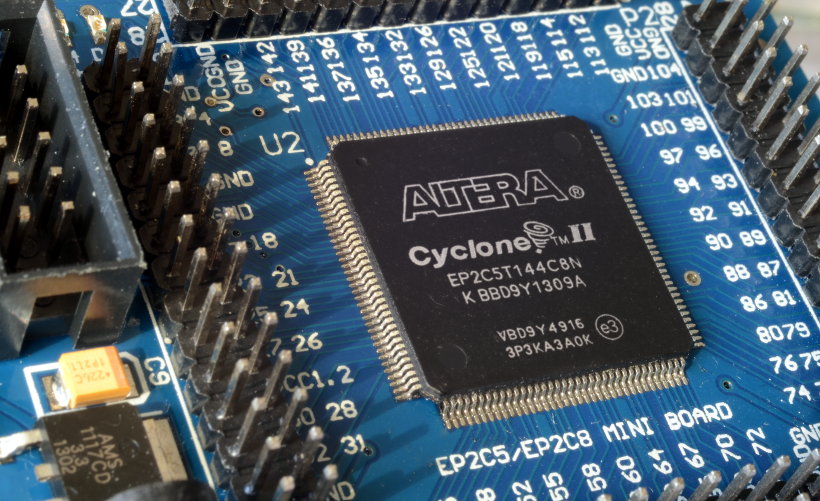

Como puede verse, los principales fabricantes son Xilinx y Altera. Mientras que la segunda ha presentado más avances (este año, 2014, empieza la producción de circuitos integrados con tecnología de 14 nm cuando Xilinx dispone de tecnología de 16 nm) el dominio en el segmento de mercado con más producción, actualmente 28 nm correspondiente a las FPGA más habituales, corresponde a Xilinx, dejando a Altera una mayor presencia en un sector tecnológico de menor nivel de integración (entre 65 nm y 90 nm, que corresponde, principalmente, a CPLD menos avanzadas)

Lenguajes de descripción de hardware (HDL)

Los lenguajes utilizados para describir los dispostivos de lógica programada se suelen llamar HDL por Hardware Description Language en inglés (lenguajes de descripción de hardware en español) o lenguajes de modelado de hardware.

Pese a que algunos HDL basan buena parte de su sintaxis en la de conocidos lenguajes de programación (C y Java, entre otros) es importante distinguirlos de ellos ya que con el HDL no se define un programa sino el comportamiento del dispositivo lógico, las conexiones que se usarán como entradas o como salidas y las operaciones lógicas que se realizan con las primeras para obtener las segundas, ya sea directamente, ya sea usando recursos intermedios, biestables, por ejemplo.

Los HDL permiten al diseñador del hardware describir el comportamiento de futuro dispositivo definiendo sus tablas de verdad, los distintos estados (en el sentido de que el dispositivo es una máquina de estado). Una de las principales diferencias entre los lenguajes de programación y los de modelado de hardware es la concurrencia inherente a los segundos y a los dispositivos que describen.

Los dos lenguajes de descripción de hardware más utilizados en la actualidad son VHDL, un poco más difundido en Europa, y Verilog, un poco más presente en América y más usado en la industria (frente al ámbito académico) y presumiblemente se asentará aún más debido a la aparición de SystemVerilog, que añade a la descripción del hardware la realización de pruebas de funcionamiento del mismo.

Los HDL permiten definir bloques de código con un comportamiento autónomo del resto de la descripción, simplificando mucho, equiparables a una función o a una clase en un lenguaje de programación. Con este recurso, además de hacer más cómoda y legible la descripción de un hardware concreto, se pueden describir operaciones genéricas, sin límite de complejidad, reutilizables en otros diseños.

A este recurso se le suele denominar soft core, por ser software, en contraposición al hard core, que representa hardware físico y no las instrucciones para su síntesis. Muchos de estos desarrollos se licencian a terceros para que los fabriquen o los incorporen a su propio hardware. Tanto los soft cores como los hard cores pertenecen a la categoría de los semiconductor intellectual property cores (SIPC), más popularmente conocidos como IP cores o IP blocks, traducibles como núcleos IP o bloques IP.

antonia

eficiente información